SPI总线电路防护方案

SPI总线为高速同步串行接口,支持全双工通信,传输速率可达10 Mbps以上,典型应用包括Flash、ADC、传感器等。SPI在芯片的管脚上占用四根线,节约芯片管脚的同时为PCB布局节约空间。SPI协议未设定速度上限,实际应用中往往能实现超过10 Mbps的传输速率,这一特性使得SPI总线成为传输未压缩音频及压缩视频等大数据量内容的理想选择。

SPI接口一般使用四条信号线通信:

MISO: 主设备输入/从设备输出引脚。该引脚在从模式下发送数据,在主模式下接收数据。

MOSI: 主设备输出/从设备输入引脚。该引脚在主模式下发送数据,在从模式下接收数据。

SCLK:串行时钟信号,由主设备产生。

CS/SS:从设备片选信号,由主设备控制。它的功能是用来作为“片选引脚”,也就是选择指定的从设备,让主设备可以单独地与特定从设备通讯,避免数据线上的冲突。

其面临的防护挑战:

1. 寄生电容需小于2pF以避免信号衰减(尤其是SCLK和MOSI/MISO高速信号线)

2. 需满足IEC 61000-4-2 Level 4(±8kV接触放电,±15kV空气放电)

3. 需同时保护SCLK、MOSI、MISO、CS四路信号线

晟驰微电子对此提供两种电路防护解决方案

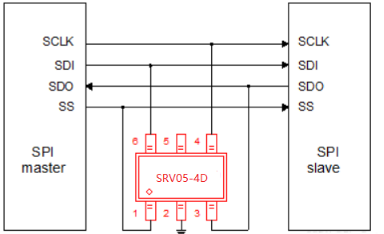

方案一:

SRV05-4D封装为SOT23-6L,有六个引脚,可同时保护SPI接口的四条通道免受静电放电(ESD)和低等级浪涌事件的冲击与干扰。该器件的工作电压为5V,结电容最大1.8pF,最大钳位电压为20V@IPP=25A,符合IEC 61000-4-2 (ESD) 规范,在 ±30kV(空气)和 ±30kV(接触)下提供瞬变保护。

SRV05-4D电气特性

| Parameter | Symbol | Min | Typ | Max | Unit | Test Condition |

| Reverse Working Voltage | VRWM | 5 | V | |||

| Breakdown Voltage | VBR | 6 | V | IT = 1mA, Pin 5 to Pin 2 | ||

| Reverse Leakage Current | IR | 0.5 | µA | VRWM = 5V, Pin 5 to Pin 2 | ||

| Forward Voltage | VF | 1.2 | V | IF = 15mA | ||

| Clamping Voltage | VC | 12 | V | IPP = 1A (8 x 20µs pulse), any I/O pin to ground | ||

| Clamping Voltage | VC | 20 | V | IPP = 25A (8 x 20µs pulse), any I/ | ||

| O pin to ground | ||||||

| Junction Capacitance | CJ | 0.45 | pF | VR = 0V, f = 1MHz, between I/O pins | ||

| Junction Capacitance | CJ | 1 | 1.8 | pF | VR = 0V, f = 1MHz, any I/O pin to ground |

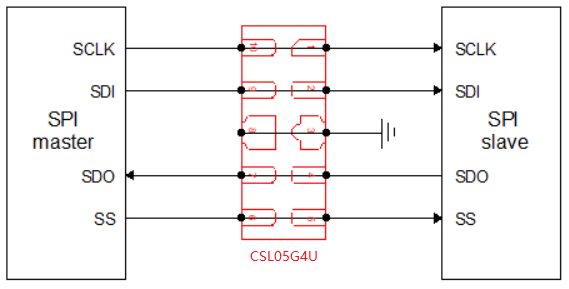

方案二:

CSL05G4U封装为DFN2510,是十引脚集成式ESD防护器件。器件的流通式封装设计简化了 PCB 布局,减少布线过程中的不连续性,促进了信号完整性和系统稳定性的提升。该器件的工作电压为5V,结电容仅为0.45PF,钳位电压为21.5V@IPP=20A,符合IEC 61000-4-2 (ESD) 规范,在 ±25kV(空气)和 ±20kV(接触)下提供瞬变保护。

CSL05G4U电气特性

| Parameter | Symbol | Conditions | Min. | Typ. | Max. | Units |

| Reverse Stand-off Voltage | VRWM | 5 | V | |||

| Reverse Breakdown Voltage | VBR | IT=1mA | 6 | V | ||

| Reverse Leakage Current | IR | VRWM=5V | 0.1 | uA | ||

| Clamping Voltage | VC | IPP=1A; tp=8/20us | 8 | V | ||

| Clamping Voltage | VC | IPP=4A; tp=8/20us | 12 | V | ||

| TLP Clamping Voltage | VC | IPL=3A; tp=0.2/100ns | 10 | V | ||

| TLP Clamping Voltage | VC | IPL=20A; tp=0.2/100ns | 21.5 | V | ||

| Dynamic resistance | Rdyn | TLP, I/O to Gnd | 0.68 | Ω | ||

| Junction Capacitance | CJ | I/O to GND; VR=0V; f=1MHz | 0.45 | pF | ||

| Junction Capacitance | CJ | I/O to IO; VR=0V; f=1MHz | 0.25 | pF |